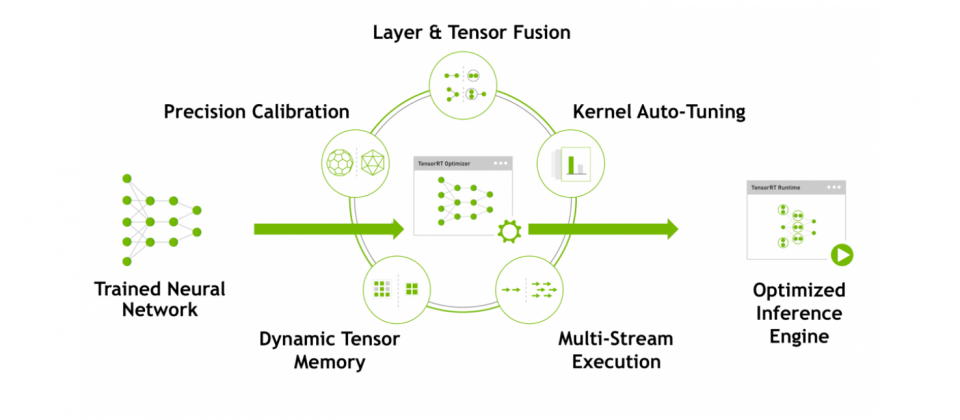

近几年来,在边缘设备上运行AI算法模型的研究以及相关设计层出不穷。笔者的课题也与该方向有一定关联,因此写下此文记录并分享,方便以后回看。一般来说,实现AI模型的运行需要2个核心部件,即控制单元和计算单元。前者一般就是MCU或者状态机等等,后者一般是DPU, VPU, TPU等叫法不一v加速器,专业名词并不重要,但其实本质都是一个高通量的阵列计算单元,包含卷积、池化、element-wise、batch-norm等operation,并具备存储和数据交互的能力。简单来说,用户配置控制单元后,控制单元将要计算的数据、与计算相关配置参数从外部存储器件读入至计算单元中,该单元计算完数据以后再将结果写入到外部存储器。若算力不支持一次算完,则调度多次即可。近几年RISC-V发展火爆,因此,本文采用计划采用一个开源的RISC-V核作为控制单元,又由于笔者此前调试过蜂鸟E203,所以控制单元采用该核,该核的具体移植使用方法和环境配置请参考《一、RISC-V 蜂鸟E203 FPGA完全移植手册》。关于计算单元,本文将采用实验室产品,由笔者所在实验室开发的多精度(支持1bit,2bit,4bit,8bit的整型乘法)脉动阵列(32×32)AI加速器。本文仅大致介绍开发思路,无开发细节。(PS. 本工程不开源,不出售,maybe以后会有流片计划)。当然,为了让读者也能够部署类似的环境,笔者会分享一些开源的设计,有兴趣的读者可以魔改拼接实现。链接如下:

risc-v:

加速器:

该AI加速器采用HLS开发,用AXI bus控制,在Xilinx家的开发板上移植较便利。

加速器已验证过的模型:MNIST, VGG16和Resnet。

哎,唉v加速器,。真没意思。

If you like my channel,please toss the coin, hit like, and favorite it.

限 时 特 惠: 本站每日持续更新海量各大内部创业教程,加站长微信免费获取积分,会员只需38元,全站资源免费下载 点击查看详情

站 长 微 信: thumbxmw